## **STATUS OF OPEN FABRICS OVER VERBS BASED FABRICS**

Sayantan Sur, Intel

Presenting work done by Arun Ilango, Dmitry Gladkov, Dmitry Durnov and Sean Hefty and others in the OFIWG community

6<sup>th</sup> Annual MVAPICH User Group (MUG) 2018

### Legal Disclaimer & Optimization Notice

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit <u>www.intel.com/benchmarks</u>.

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Copyright © 2018, Intel Corporation. All rights reserved. Intel, Pentium, Xeon, Xeon Phi, Core, VTune, Cilk, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804

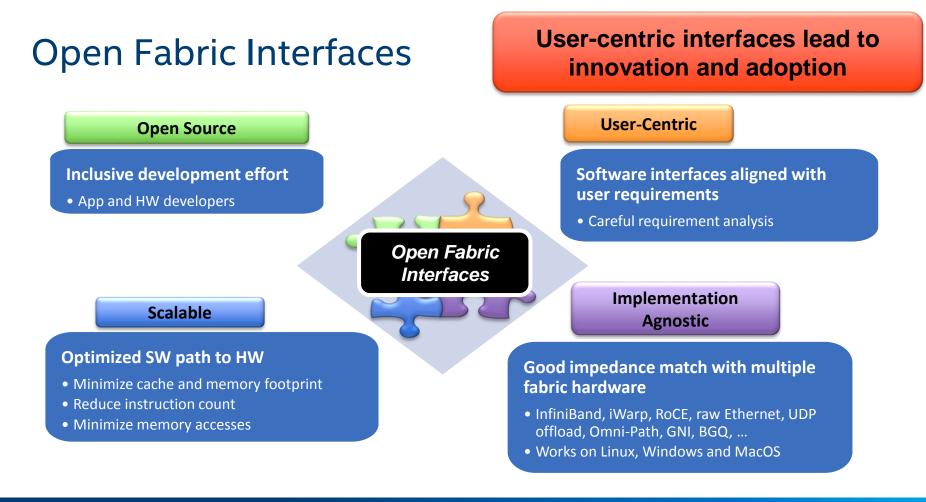

#### OFI – State of the Union

#### **OFI Insulates applications** from wide diversity of fabrics underneath

|                                                | Intel <sup>®</sup> MPI<br>Library               |  | APICH* Cha                         |                            | n++*                    | Open M | Open MPI*                |                                   | t*        | Sandia<br>SHMEM*             | N                            | letIO* | Intel <sup>®</sup> MLSL                      | #  |  |

|------------------------------------------------|-------------------------------------------------|--|------------------------------------|----------------------------|-------------------------|--------|--------------------------|-----------------------------------|-----------|------------------------------|------------------------------|--------|----------------------------------------------|----|--|

|                                                | libfabric Enabled Middleware                    |  |                                    |                            |                         |        |                          |                                   |           |                              |                              |        |                                              |    |  |

| OFI<br>Advanced application oriented semantics |                                                 |  |                                    |                            |                         |        |                          |                                   |           |                              |                              |        |                                              |    |  |

|                                                | Tag Matching                                    |  | Scalable<br>memory<br>registration |                            | Triggered<br>Operations |        | Со                       | Remote<br>Completion<br>Semantics |           | Multi-<br>Receive<br>buffers | Shared<br>Address<br>Vectors |        | Unexpected<br>Message<br>Buffering           |    |  |

|                                                | Streaming Endpoints Reliable Datagram Endpoints |  |                                    |                            |                         |        |                          |                                   | points    |                              |                              |        |                                              |    |  |

|                                                | Sockets<br>TCP, UDP                             |  | S                                  | Cisco<br>sNIC <sup>*</sup> |                         |        | Cray<br>GNI <sup>*</sup> |                                   | Mellanox* |                              | IBM Blue<br>Gene*            |        | Exciting new<br>providers in<br>development! |    |  |

|                                                |                                                 |  |                                    |                            |                         |        |                          |                                   |           |                              |                              |        | # Exploratio                                 | on |  |

\* Other names and brands may be claimed as property of others

**MUG** '18

#### **OFI Implementation Update**

- ✓ OFI Provider Infrastructure

- ✓ OFI API Exploration

- ✓ Companion APIs (Bonus!)

#### 1.5 API Updates

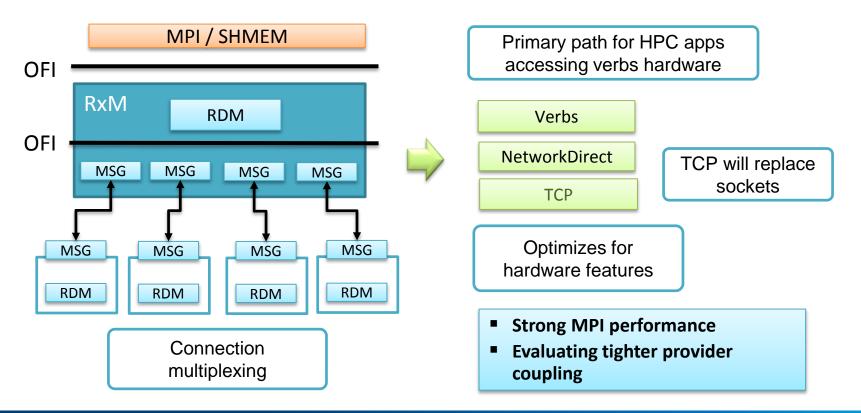

- RxM provider

- SOCK endpoint types

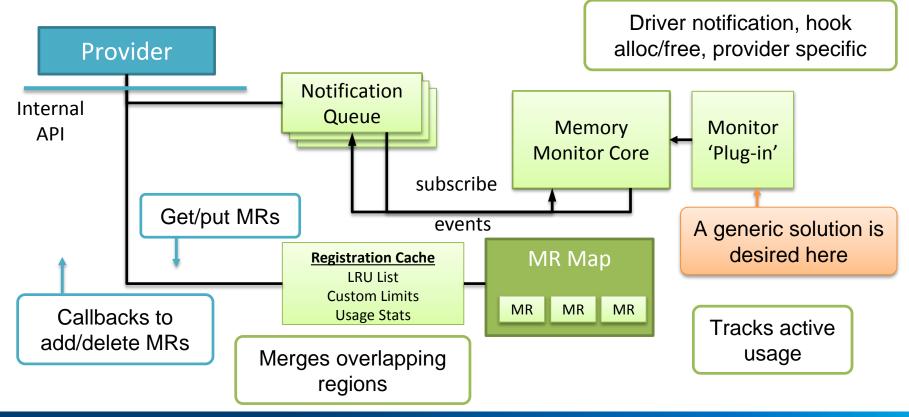

- Memory registration

- API optimizations

2017

v1.4.0..

..1.4.2

v1.5.0..

..1.5.3

2018

v1.6.0..

v1.6.1

v1.6.2

v1.7.0

#### **1.6 Provider Enhancements**

- PSM2 native

- RxM performance

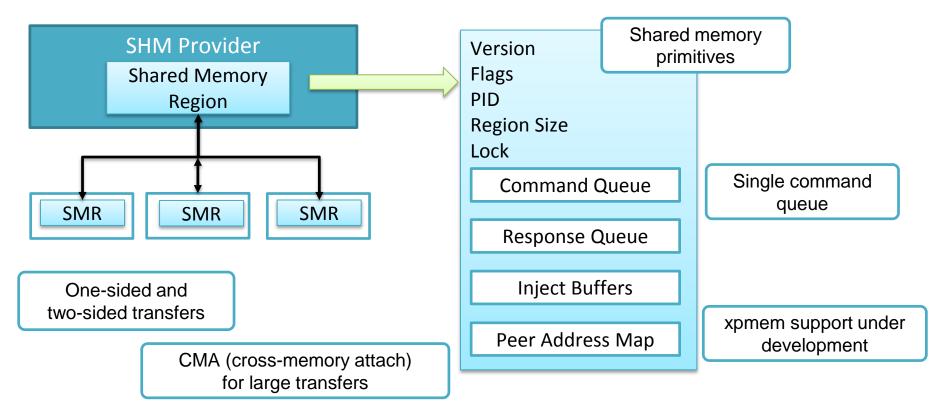

- SHM shared memory support

- Persistent memory

#### **1.7 Predictions**

- New providers

- RxD, multi-rail, new vendors

- SHM xpmem support

- API enhancements

## Provider Infrastructure Updates

### RXM – Reliable Datagrams over Connections

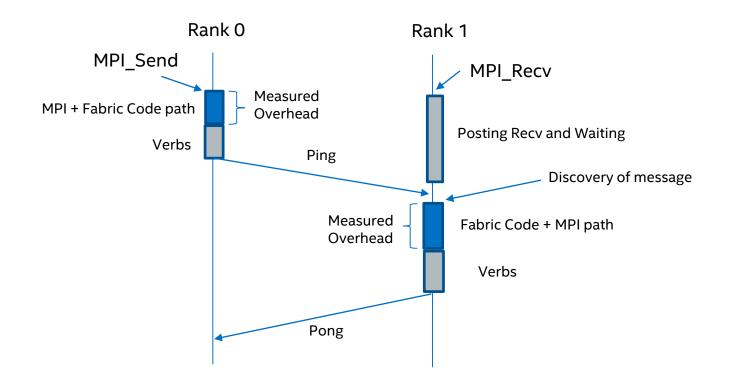

### MPI Critical Path Software overhead Analysis

### MPI Critical path software overhead

#### Critical SW Code Path for Ping Pong Test

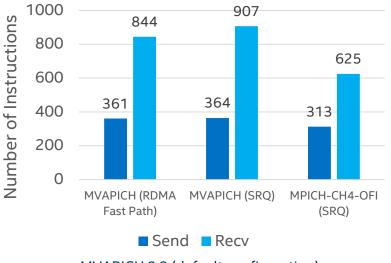

MVAPICH 2.3 (default configuration) GCC 4.8.5, OFI master (@585919d) -O3, -DNDEBUG Gains in total code path primarily coming from combination MPICH-CH4 and OFI RXM provider

Instruction counts are an indirect measure help us gauge semantic fit

**Ongoing optimization**

• Aiming to reduce send path to about 250 instructions, and receive path to 450-480 instructions

Similar optimizations are possible in MVAPICH

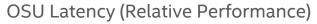

### **MPI Performance Analysis - Latency**

#### Platform:

Intel(R) Xeon(R) CPU E5-2699 v4 @ 2.20GHz Infiniband controller: Mellanox Technologies MT27700 Family [ConnectX-4] intel\_pstate on/turbo on RHEL 7.4 mlnx1-OFED.4.3.0.2.1.43101.x86\_64

#### Run details:

\$ mpirun -hosts nnlmpibdw01,nnlmpibdw02 -n 2 -ppn 1 numactl --physcpubind=7 osu\_latency -i 40000

\$ FI\_OFI\_RXM\_SAR\_LIMIT=8192 FI\_VERBS\_MR\_CACHE\_ENABLE=1 mpirun -hosts nnlmpibdw01,nnlmpibdw02 -n 2 -ppn 1 numactl -physcpubind=7 osu\_latency -i 40000

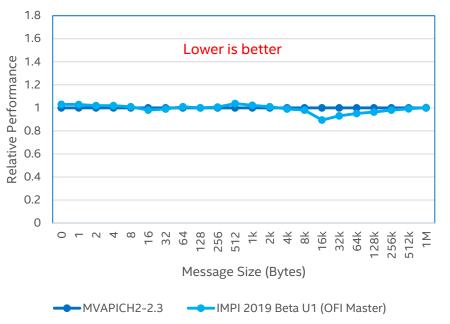

### MPI Performance Analysis – Message Rate

#### OSU Messaging Rate (Relative Performance)

#### Platform:

Intel(R) Xeon(R) CPU E5-2699 v4 @ 2.20GHz Infiniband controller: Mellanox Technologies MT27700 Family [ConnectX-4] intel\_pstate on/turbo on RHEL 7.4 mlnx1-OFED.4.3.0.2.1.43101.x86\_64

#### Run details:

\$ mpirun -hosts nnlmpibdw01,nnlmpibdw02 -n 2 -ppn 1 numactl --physcpubind=7 osu\_mbw\_mr

\$ FI\_OFI\_RXM\_SAR\_LIMIT=8192 FI\_VERBS\_MR\_CACHE\_ENABLE=1 mpirun -hosts nnlmpibdw01,nnlmpibdw02 -n 2 -ppn 1 numactl -physcpubind=7 osu\_mbw\_mr

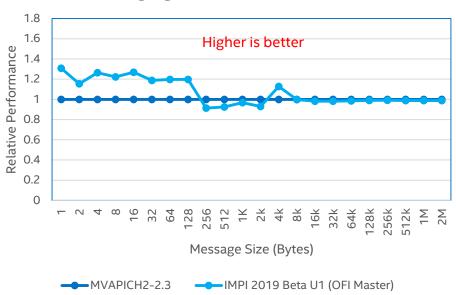

### RXD – Reliable Datagram over Unreliable Datagram

### **Shared Memory Provider**

intel

### Memory Monitor and Registration Cache

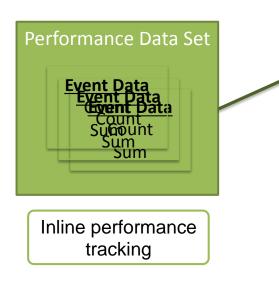

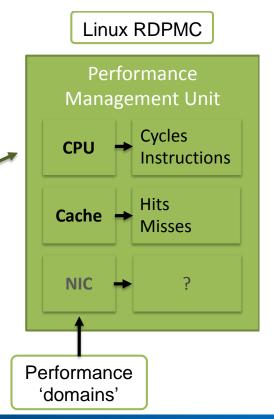

## **Performance Monitoring**

Ex: Sample CPU instructions for various code paths

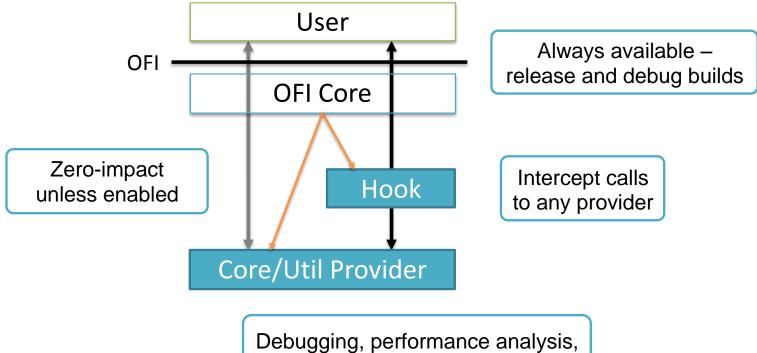

### **Hooking Provider**

feature enhancements, testing

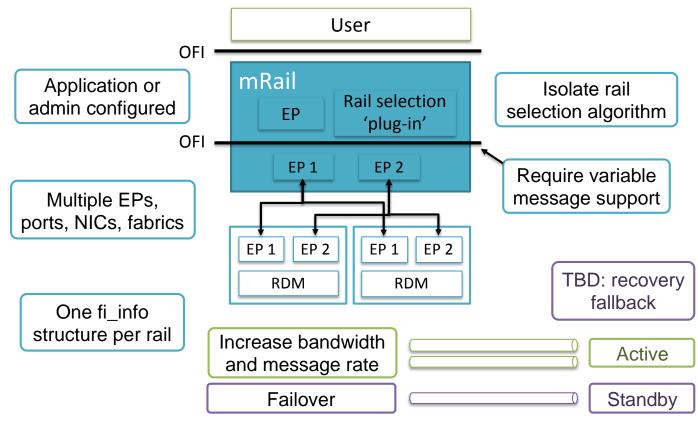

## Multi-rail provider

## **API Exploration**

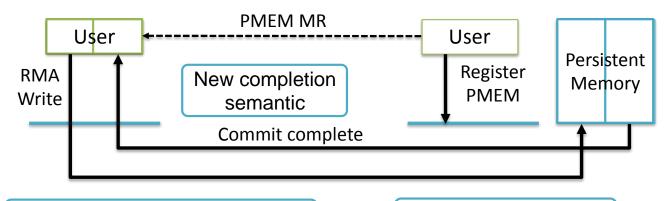

### **Persistent Memory**

Work with SNIA (Storage Networking Industry Association)

Evolve APIs to support other usage models

#### Exploration

- Byte addressable or object aware

- Single or multi-transfer commit

- Advanced operations (e.g. atomics)

- Keep implementation agnostic

- Handle offload and on-load models

- Support multi-rail

- Minimize state footprint

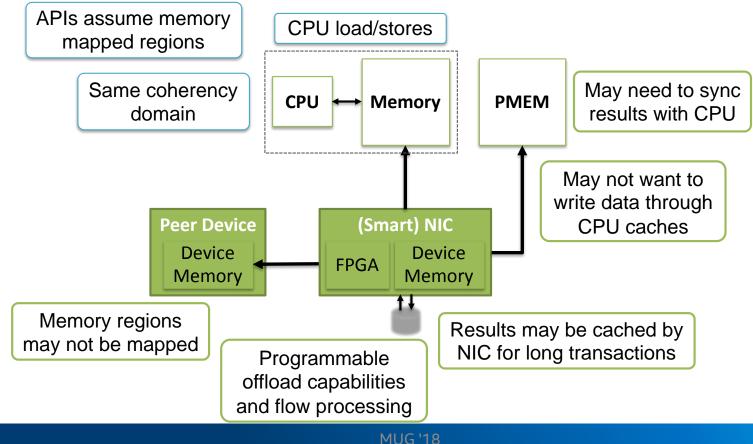

#### **Data Domains**

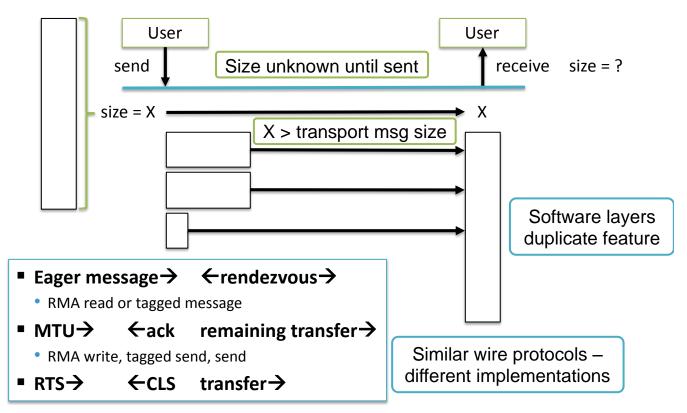

## Variable Length Messages

### Variable Length Messages (continued)

## **Companion APIs**

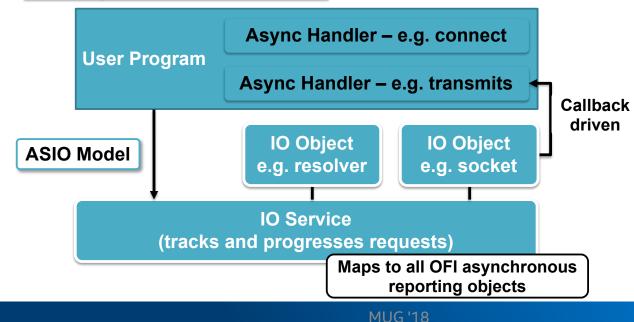

### C++ Standardization

# Add support for fabrics directly to the C++ language

#### Feedback from C++ community

- Implement proposal

- Detail alternatives

- Justify extensions

#### Proposal

- Extend ASIO

- Implement over libfabric

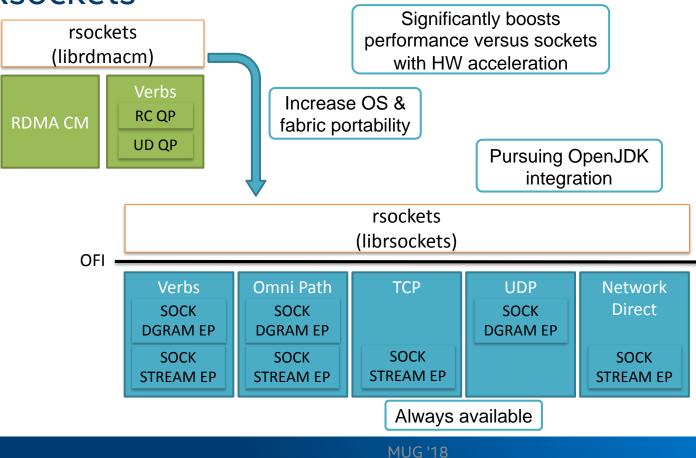

#### Rsockets

Significant software work ongoing to implement full set of OFI features on Fabric providers that lack native support

Components developed are generic and re-usable across Fabrics

Fabric vendors can implement subset of features and get access to wide OFI software ecosystem by leveraging utility components

As newer features are added to OFI, provide a pathway to quickly enable those features in older providers – applications can track latest OFI APIs

Participation in OFIWG is free, simple, no associations or boards to join

http://libfabric.org