# HPC Network Stack Update

Pavel Shamis/Pasha, Principal Research

Engineer

MVAPICH User Group Meeting 2018 Columbus, OH

# **RDMA Update**

© 2017 Arm Limited

### **VERBs API on Arm**

- Besides bug fixes not much work was required

- Mellanox OFED 2.4 and above supports Arm

- Linux Kernel 4.5.0 and above (maybe even earlier)

- Linux Distribution Support on going process

- OFED no official ARMv8 support

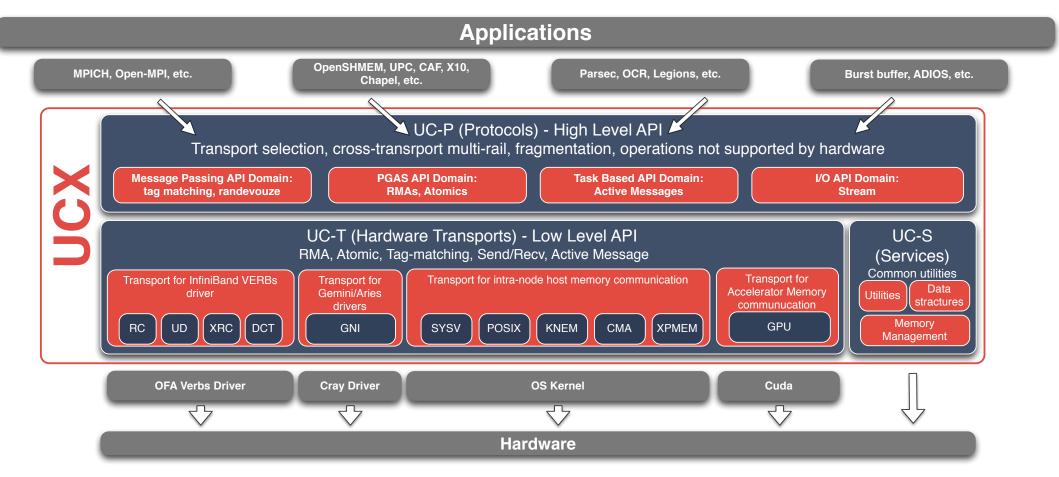

### **OpenUCX**

#### WWW.OPENUCX.ORG

https://github.com/openucx/ucx

arm

#### UCX 1.3: <a href="https://github.com/openucx/ucx/releases/tag/v1.3.0">https://github.com/openucx/ucx/releases/tag/v1.3.0</a>

- Multi-rail support for eager and rendezvous protocols

- Added stream-based communication API

- Added support for GPU platforms: Nvidia CUDA and AMD ROCM software stacks

- Added API for Client-Server based connection establishment

- Added support for TCP transport (Send/Receive semantics)

- Support for InfiniBand hardware tag-matching for DC and accelerated transports

- Added support for tag-matching communications with CUDA buffers

- Initial support for Java bindings

- Progress engine optimizations

- Improved scalability of software tag-matching by using a hash table

- Added transparent huge-pages allocator

- Added non-blocking flush and disconnect semantics

- Added registration cache for KNEM

- 5 © 2017 Arm Limited

### **UCX Roadmap**

#### v1.4 – end of <del>July</del> August

- Bitwise atomics support

- Improvements for message injection (medium message size)

- Client/server connection establishment to support large address

- Support multiple connections between same pair of endpoints

- CUDA-IPC support

#### v1.5 – November 2018

- Bugfixes and optimizations

- Active Message API

- New Client-Server API

- Full functionality over TCP

- Full functionality over legacy RDMA devices

- Full functionality over uGNI API

- V2.0-2019

- Updated API not backward compatible with 1.x

- Binary distribution will provide v1.x version of the library (in addition for 2.x) for backward compatibility

- All codes should work as it is

# MPI

© 2017 Arm Limited

### Scaling

•

CAVIUM

THUNDERX

penMP

University of BRISTOL GW4 January 17th 2017 Announcing the GW4 Tier 2 HPC service, 'Isambard': named after Isambard Kingdom Brunel System specs: Cray CS-400 system • 10,000+ ARMv8 cores · HPC optimised software stack · Technology comparison: • x86, KNL, Pascal To be installed March-Dec 2017 • £4.7m total project cost over 3 years McIntosh Smith, simonm@cs.bris.ac.uk, Sandia's NNSA/ASC ARM Platforms = 2015 = 2017 = 2018

GCC

8 © 2017 Arm Limited

### **Programing models**

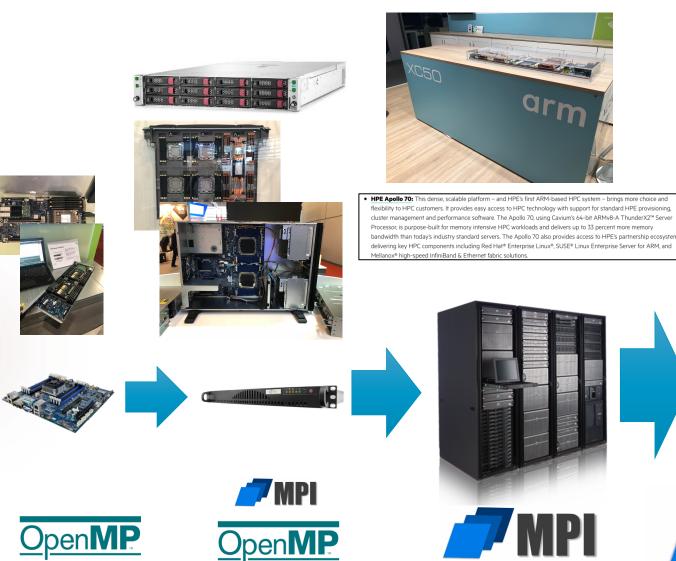

#### MVAPICH 2.3 – works on ARMv8

MPICH 3.3b – works on ARMv8

Open MPI 3.x – works on ARMv8

OSHMEM – work on ARMv8

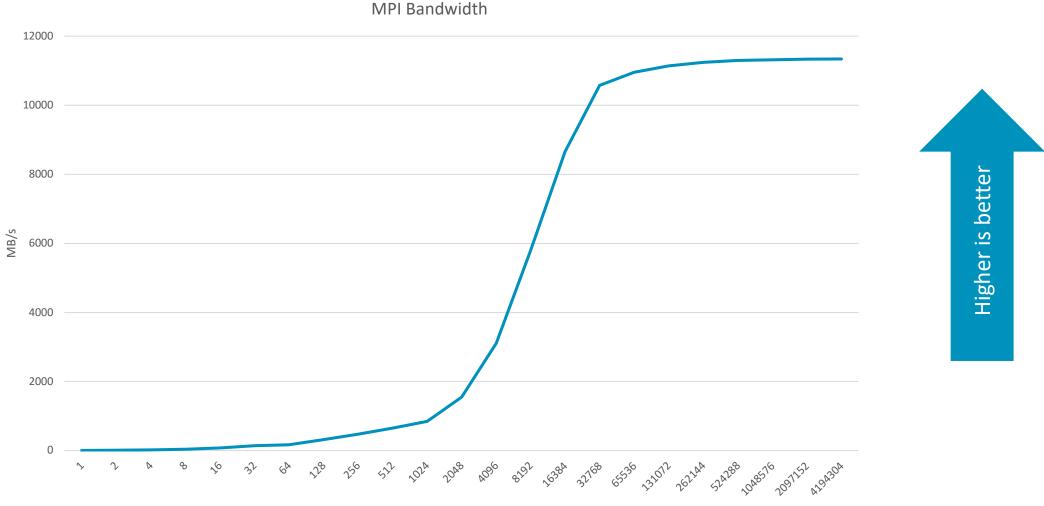

#### HPE Comanche (Apollo 70) with Cavium Thunder X2 SINGLE core, Mellanox ConnextX-4 100Gb/s (EDR) - Bandwidth

Message Size

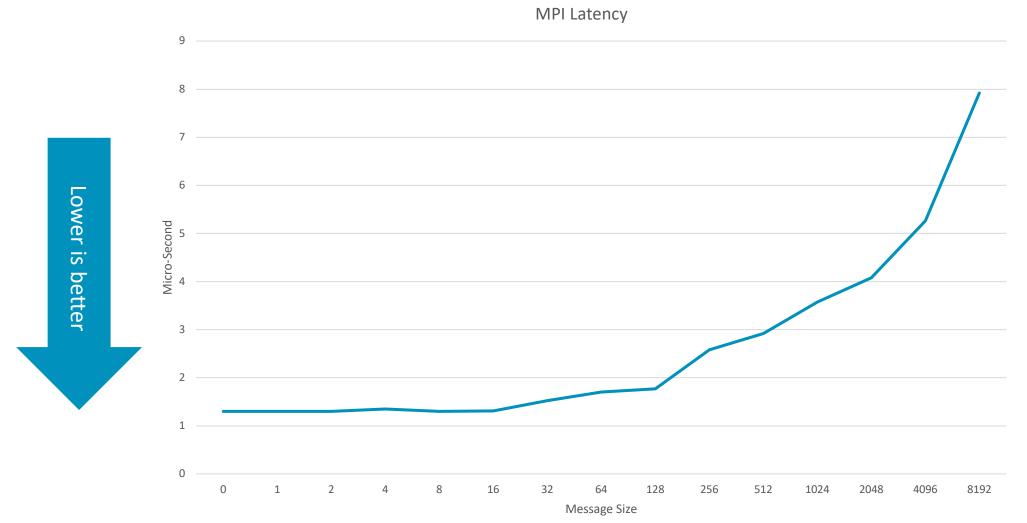

#### HPE Comanche (Apollo 70) with Cavium Thunder X2, Mellanox ConnectX-4 100Gb/s (EDR) – Latency/Ping Pong

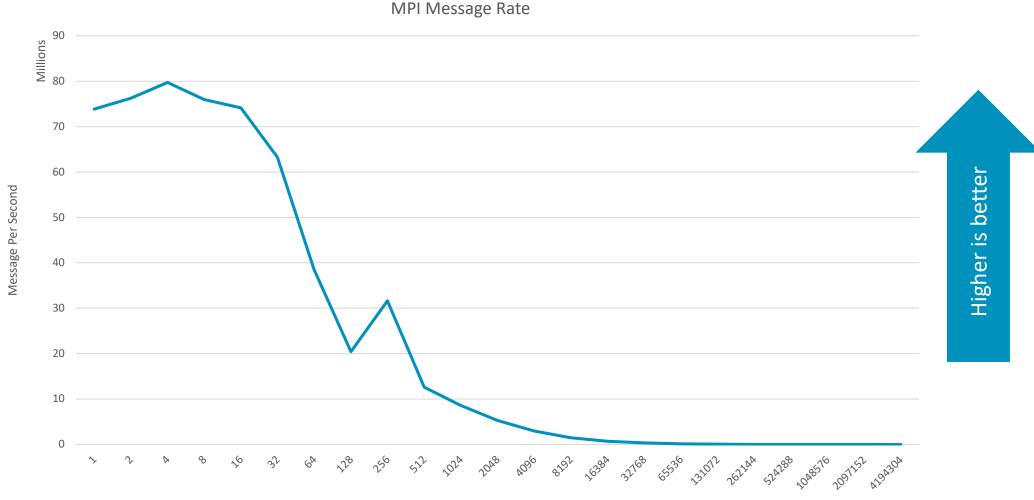

#### HPE Comanche (Apollo 70) with Cavium Thunder X2, Mellanox ConnectX-4 100Gb/s (EDR) – MPI Message Rate (28 cores)

Message Size

# **MVAPICH Update**

© 2017 Arm Limited

### **Building with Arm compiler**

#### Example:

*my\_cc=armclang*

my\_cxx=armclang++

my\_fc=armflang

../configure CC=\${my\_cc} CXX=\${my\_cxx} F77=\${my\_fc} FC=\${my\_fc} --prefix=\$INSTALL\_DIR --withdevice=ch3:mrail --with-rdma=gen2 --enable-cxx --enable-fc

#### Post configure fix for libtool (it does not get the right flags for armflang):

sed -i -e 's#wl=""#wl="-Wl,"#g' libtool

sed -i -e 's#pic\_flag=""#pic\_flag=" -fPIC -DPIC"#g' libtool

Arm Allinea Studio 18.4 release is now available on developer.arm.com

### Weakly Ordered Memory Model

Weakly ordered memory access means that changes to memory can be applied in any order as long as *single-core* execution sees the data needed for program correctness

Benefits:

- The processor can make many optimizations to reduce memory access

- This has power (pushing bits is expensive) and memory bandwidth benefits

- The optimizations are transparent to single-core execution

#### Challenges:

- Synchronization of data between cores must be explicit

- Popular legacy architectures (EG: x86\_64, x86) provide "almost" strongly ordered memory access

- This means that existing multi-core codes may be dependent on strongly ordered accesses

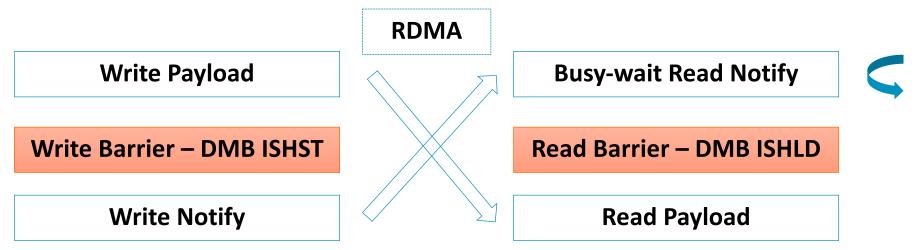

### **Memory Barriers on Arm**

#### **Memory Barriers**

- Multithread environment

- Software-hardware interaction

- Examples <u>https://github.com/openucx/ucx/blob/master/src/ucs/arch/aarch64/cpu.h#L25</u>

- You can "fish" for these bugs in MPI implementations around Eager-RDMA and shared memory protocols

Maranget, Luc, Susmit Sarkar, and Peter Sewell. "A tutorial introduction to the Arm and POWER relaxed memory models." Draft available from http://www. cl. cam. ac. uk/~ pes20/ppc-supplemental/test7. pdf (2012).

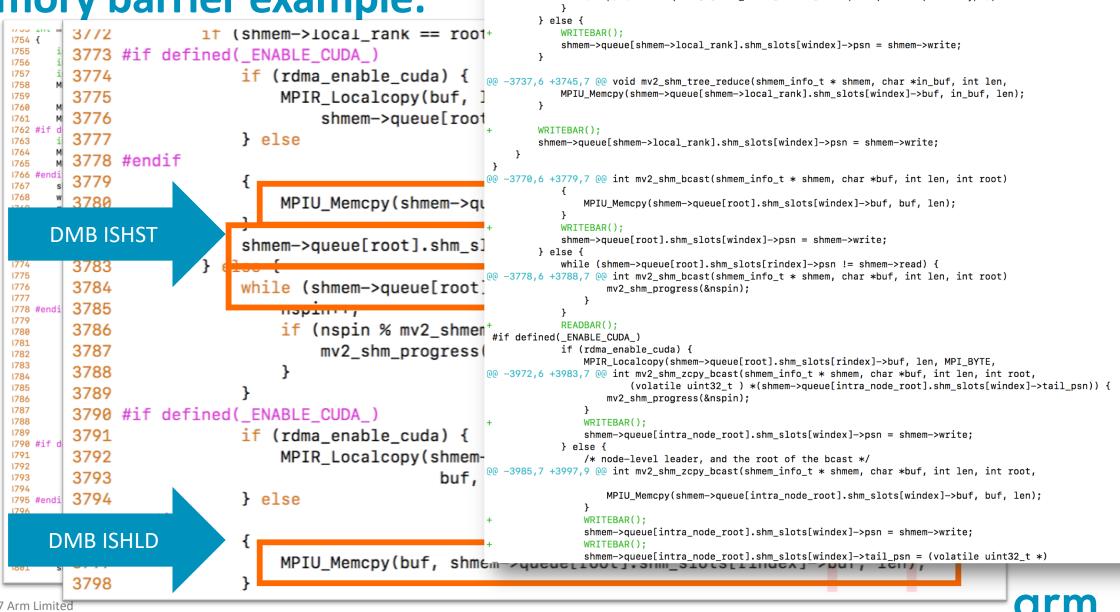

### **Memory barrier example:**

11 (1S\_CXX\_UOD) 1

(\*MPIR\_Process.cxx\_call\_op\_fn) (

QQ -3723,6 +3730,7 QQ void mv2\_shm\_tree\_reduce(shmem\_info\_t \* shmem, char \*in\_buf, int len,

(\*uop) (shmem->queue[i].shm slots[rindex]->buf, buf, &count, &datatype);

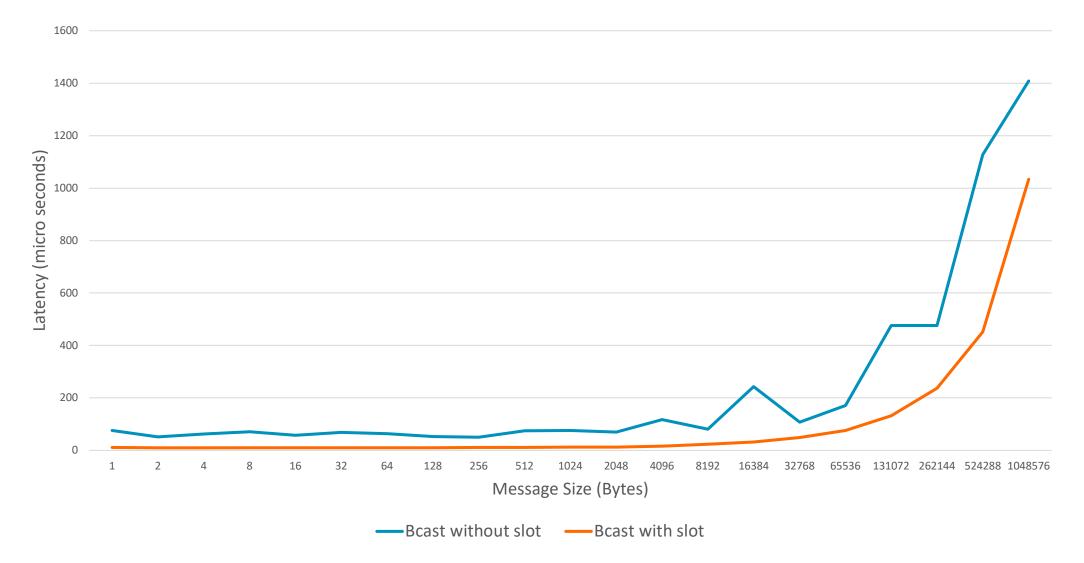

#### **OSU MVAPICH BCAST (448 processes)**

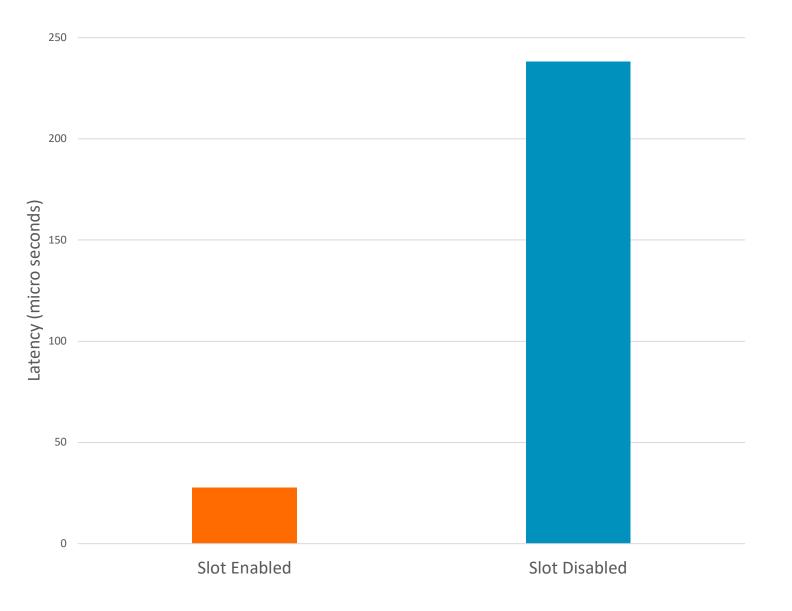

#### **OSU MVAPICH Barrier (448 processes)**

## HPCAC - http://hpcadvisorycouncil.com/

Juno

#### 1x GIGABYTE R270-T64 Chassis

- 2 x Cavium ThunderX 48-core ARM processors

- Memory: 64GB DDR4 2400 MHz

- Mellanox ConnectX-4 EDR 100Gb/s InfiniBand/VPI adapter

- SSD 480GB SATA 3

- 2x GIGABYTE MT30-GS0 Chassis

- 1x Cavium ThunderX 32-core ARM Processor

- Memory: 128GB DDR4 2400 MHz

- Mellanox ConnectX-5 EDR 100Gb/s InfiniBand/VPI adapter

- SSD 1TB SATA 3

Switch : Mellanox Switch-IB 2 SB7800 36-Port 100Gb/s EDR

InfiniBand switches

Apply for System Access

# arm

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks

Thank You! Danke! Merci! 谢谢! ありがとう! **Gracias!** Kiitos! 감사합니다 धन्यवाद

# arm